Ainekko acquired Esperanto Technologies’ intellectual property in October 2025 after Esperanto closed in July 2025 due to staff attrition. Ainekko open-sources the ET-SoC-1 chip design, a many-core RISC-V architecture with over 1,000 cores, redirecting it from data center applications to edge computing. The company releases RTL, tools, and documentation under Apache License v2 through its AI Foundry platform, enabling developers to build custom AI inference hardware for robotics, industrial automation, IoT, and embedded applications.

Esperanto Technologies, established in 2014, achieved RTL completion for its Maxion CPU line in September 2018. The company advanced to the bring-up and silicon characterization phase for its ET-SoC-1 during the latter half of 2021, while next-generation ET-SoC-2x and ET-SoC-3x platforms were presented in November 2024. Esperanto closed most of its operations in July 2025, maintaining only essential personnel to facilitate intellectual property transactions. According to internal statements, intense competition from rival firms, which offered prospective employees compensation up to four times higher than Esperanto’s packages, contributed to a persistent loss of talent. Industry assessments also point to suboptimal market engagement, as Esperanto’s commercial platform limited access to evaluation requests rather than immediate procurement and pricing, possibly constraining commercial traction.

Ainekko launched publicly in October 2025, presenting the et-platform and et-man repositories through GitHub. These resources provide an open simulation environment, kernel drivers, firmware, and management software, along with an extensive programmer’s reference. Subsequent documentation releases are anticipated to add detail. Ainekko acquired Esperanto’s intellectual property foundation, encompassing all hardware and software development assets. Plans include releasing RTL code to the open-source community, with third-party licensed IP modules such as PCIe controllers excluded in accordance with licensing terms.

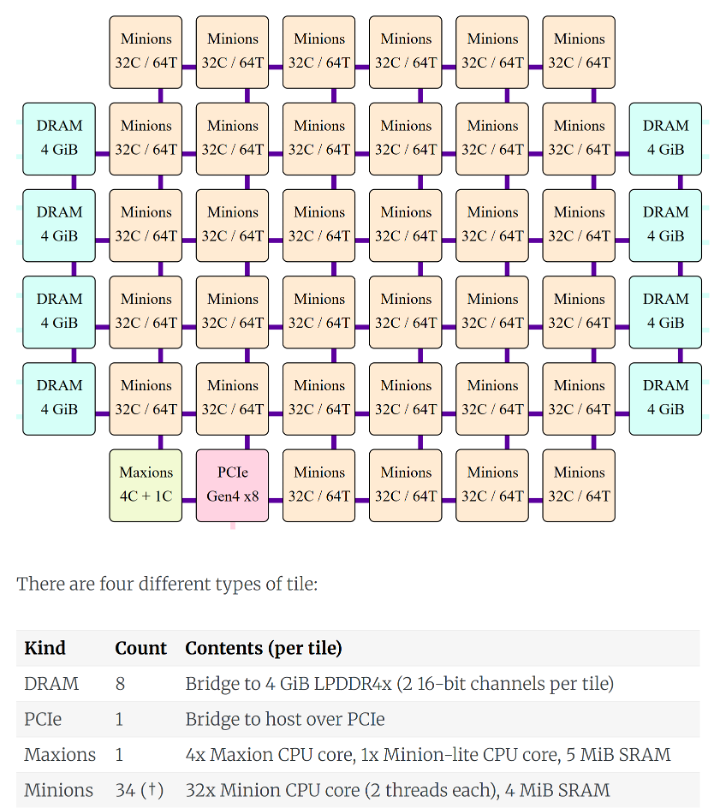

The ET-SoC-1 introduces a densely integrated, many-core RISC-V system-on-chip, incorporating over 1,000 Minion cores on a single die. The design allows instruction-level programmability and supports heterogeneous workloads, including AI and high-performance data center applications, as well as general-purpose computation. Esperanto’s engineering efforts prioritized large-scale parallel processing and optimized energy use, with the technical deliverable demonstrating the feasibility of high-performance, open-source multi-core implementations within recognized physical and power constraints.

Figure 1. Esperanto’s multi-core AI processor. (Source: Esperanto)

As the new steward of this technology, Ainekko has prioritized reorienting the system toward edge deployments. This focus leverages the energy efficiency and architectural modularity inherent in the design, providing solutions for robotics, autonomous navigation,

industrial automation, secure embedded monitoring, and other AI-powered inference workloads at the microcontroller and system-on-chip scale. The open-technology Foundation supports academic research and prototyping, while offering a pathway for domain-specific SoC customization and high-throughput media processing.

Through its AI Foundry, Ainekko extends a collaborative, open-source engagement model from software to hardware. The company seeks to build a participatory ecosystem, promoting transparency and shared governance over the technology stack. This transition preserves Esperanto’s original engineering accomplishments while introducing a revised market and development approach, making high-density RISC-V AI hardware available for open community use. The model emphasizes system adaptability and supports collaborative innovation in low-power, parallel inference systems.

Commentary from industry analysts identifies the project as a significant open-source silicon initiative, citing both its parallel architecture and emphasis on system efficiency. The technical platform invites deeper experimentation in custom silicon for AI tasks, particularly where the constraints of edge deployment environments set stringent power and flexibility requirements. The revised strategy preserves much of the architectural merit and demonstrates the continued evolution of open hardware for collaborative RISC-V AI development.

LIKE WHAT YOU SAW HERE? SHARE THE EXPERIENCE, TELL YOUR FRIENDS.