Renesas has introduced three new automotive SoC technologies targeted at automotive multi-domain ECUs for the software-defined vehicle (SDV) era. The company claims that the technologies boost AI performance, safety, and efficiency in SDVs. The chiplet-based architecture supports ASIL D functional safety, while advanced AI and clock designs maintain automotive-grade quality even at 3 nm. Fine-grained power control across 90-plus power domains cuts voltage drop and improves reliability. These innovations debut in the R-Car X5H SoC, enabling next-gen autonomous driving, digital cockpit, and connected-car features.

Renesas Electronics Corp. has created three new SoC technologies for automotive multi-domain electronic control units (ECUs). The company showed the three complementary automotive parts at the International Solid-State Circuits Conference 2026 (ISSCC 2026) and claims they address computation, safety, and power management needs in software-defined vehicles. The technologies target multi-domain ECUs that consolidate automated driving, cockpit, and connectivity workloads into a centralized architecture. Each technology contributes a specific mechanism: chiplet-based functional safety support, timing-aware AI processing at a 3 nm process node, and granular power-domain control with integrated monitoring. Together they form the foundation of the R-Car X5H SoC and its role in future vehicle platforms.

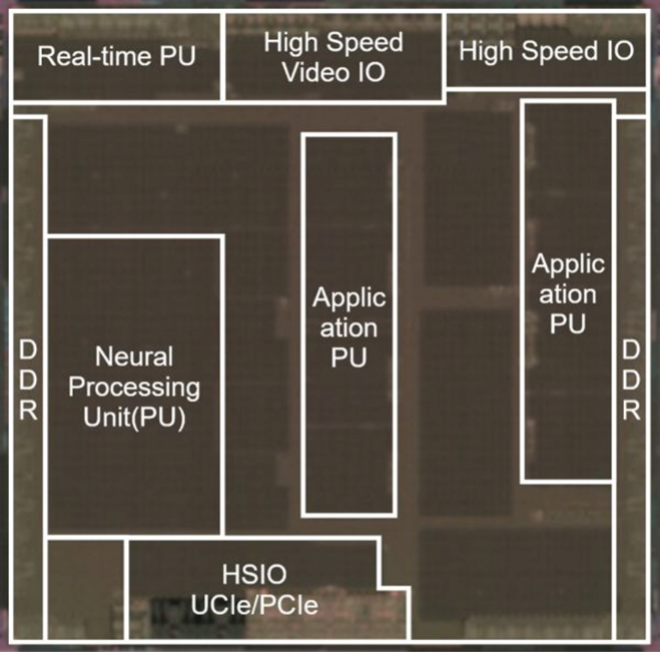

Figure 1. Block diagram of Renesas’ SoC. (Source: Renesas)

The first part has a chiplet architecture that the company says preserves functional isolation while multiple applications share common compute and memory resources. Renesas combines a standard UCIe die‑to‑die interconnect with a RegionID scheme that tags memory and bus transactions by domain. Hardware in the fabric and memory management units interpret those tags and block unauthorized cross‑domain accesses, which supports Freedom from Interference and ASIL D requirements in a multi‑die environment. This approach, as Renesas claims, lets designers scale AI accelerators or domain-specific logic through chiplets, without relaxing safety guarantees for brake control, steering, or other critical functions.

The second part focuses on AI processing and clock distribution at the 3 nm node. Neural processing units occupy a large fraction of die area and operate at high frequencies, which introduces clock latency and skew between shared sources and distributed logic. Renesas restructures the clock system into a hierarchy of mini clock pulse generators placed near sub‑modules, shortening the path length and tightening timing margins. Test circuits share the same hierarchy, so user clocks and test clocks traverse a unified path during diagnosis and production screening. This arrangement maintains deterministic timing for AI workloads, supports structural test coverage, and preserves automotive-grade reliability expectations on a large multi-domain device.

The third part implements power control and monitoring over more than 90 power domains. Domains can operate over milliwatt to multi‑watt ranges, allowing the SoC to disable inactive blocks or scale performance with workload demand. Power switches in each domain divide into ring and row elements: Ring switches manage inrush current when a domain starts, and row switches equalize impedance across the logic area to limit IR drop. Measurements indicate a reduction in voltage drop relative to earlier layouts, which supports stable operation at advanced geometries. Additional circuitry, including dual-core lockstep with independent power controllers and digital voltage monitors resistant to temperature drift, detects faults in both logic and power delivery paths.

Renesas integrates these three technologies into the R-Car X5H SoC, produced on a 3 nm automotive process and positioned as the compute core for multi-domain ECUs. The device combines application processors, real-time cores, GPUs, AI accelerators, and chiplet expansion interfaces on one platform. Vehicle manufacturers can map automated driving algorithms, digital cockpit graphics, and secure gateway functions onto isolated domains while reusing a consistent hardware and software stack. The architecture supports current driver-assistance functions and leaves capacity for later software features, aligning with the broader shift toward centralized compute in automotive electrical and electronic design.

What do we think?

Taken together, these trends point to a clear direction for automotive compute. As vehicles become software-defined, their SoCs must deliver the performance to host many concurrent applications, the scalability of chiplet-based designs, and adherence to strict functional safety targets. Growing multi-domain central processors also strain traditional approaches to quality and power, since higher performance directly drives up complexity and energy use. In response, Renesas has introduced new SoC technologies that explicitly address these demands in performance, safety, scalability, and efficiency.

JPR maintains an updated database of AIP suppliers that is part of its AI Processors Market Development report. The report is also available bundled with JPR’s AI Processor series update reports.

LIKE WHAT YOU SAW HERE? SHARE THE EXPERIENCE, TELL YOUR FRIENDS.