Intel unveiled its upcoming Intel Xeon product lineup at the Hot Chips event, introducing a novel platform architecture. It includes processors featuring the new Efficient-core (E-core) architecture alongside the established Performance-core (P-core) architecture. Code-named Sierra Forest and Granite Rapids, respectively, these products, says Intel, aim to simplify and enhance customer experiences by offering a compatible hardware architecture and shared software stack, catering to critical tasks like artificial intelligence.

What do we think? According to this announcement, Intel’s data center road map and offerings are back on track for timely delivery. Fifth-generation Intel Xeon processors (code-named Emerald Rapids) are sampling with customers and expected to launch in the fourth quarter of 2023. Intel says its Xeon processors with E-cores (Sierra Forest) are on track for delivery in the first half of 2024. Intel Xeon processors with P-cores (Granite Rapids) will follow shortly thereafter. Intel Agilex 9 Direct RF FPGAs were delivered to BAE Systems six quarters ahead of schedule.

Intel provides more details on its Sierra Forest (E-core) and Granite Rapids (P-core) Xeon processors

At Hot Chips, Intel detailed the Xeon platform architecture, providing technical specifications and features for the 2024 Xeon offerings, along with insights into the upcoming 5th Gen Intel Xeon processors. An additional session highlighted new capabilities of Intel Agilex 9 Direct RF-series FPGAs.

The platform leverages modular SoCs for scalability, flexibility, and efficiency, catering to AI, cloud, and enterprise needs. This architecture, says the company, offers socket-compatible processors, P-core and E-core, with shared intellectual property and software stacks, facilitating interchangeability for various workloads. Features include high-bandwidth Multiplexer Combined Ranks (MCR) DIMMs, Intel Flat Memory for seamless data movement, CXL 2.0 support, advanced I/O with PCIe 5.0/CXL 2.0 lanes, and up to six UPI links.

E-core processors (Sierra Forest) focus on power-efficient compute density, boasting 2.5× better rack density and 2.4× higher performance per watt. They support 1S and 2S servers with up to 144 cores per CPU, offering a modern instruction set, robust security, and memory RAS features.

P-core processors (Granite Rapids) emphasize cost-effective high-core performance for AI and general-purpose compute workloads. With 2×–3× better performance, claims the company, for mixed AI workloads, enhanced Intel AMX, higher memory bandwidth, and socket scalability up to eight sockets, they cater to diverse needs.

- P-core and E-core are delivered with shared intellectual property (IP), firmware, and OS software stack.

- Fastest DDR and new high-bandwidth MCR DIMMs.

- New Intel Flat Memory enables hardware-managed data movement between DDR5 and CXL memory, making total capacity visible to the software.

- CXL 2.0 support for all device types with backward compatibility to CXL 1.1.

- Advanced I/O with up to 136 lanes of PCIe 5.0/CXL 2.0 and up to six UPI links.

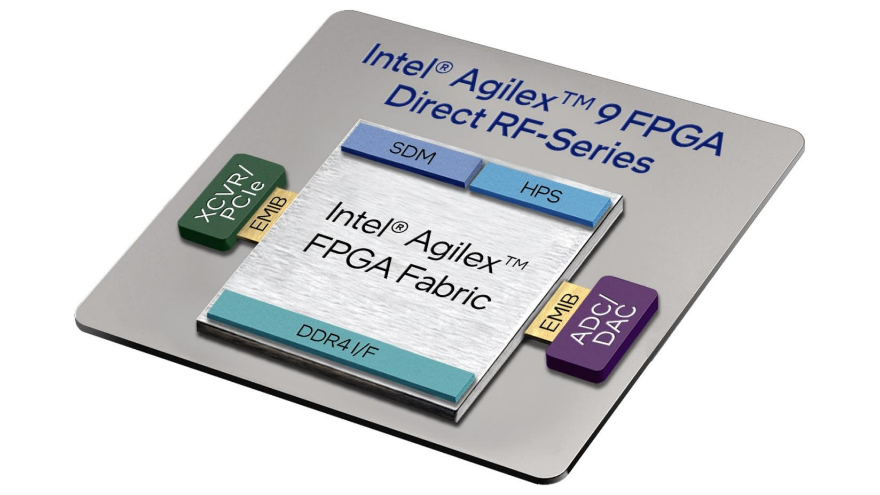

Intel Agilex 9 Direct RF-series FPGAs integrate 64Gs/s (giga-samples per second) data converters and a wideband reference design featuring both wideband and narrowband receivers within the same package. These advancements, says the company, reinforce Intel’s commitment to timely delivery in its data center road map, with products like the 5th Gen Intel Xeon processors, E-core processors, and P-core processors all on track for release. Furthermore, Intel says the early delivery of Intel Agilex 9 Direct RF FPGAs showcases Intel’s rapid capabilities through chiplet-based heterogeneous integration.

This, says Intel, demonstrates its ability to rapidly provide industry-leading capabilities via chiplet-based heterogeneous integration powered by Intel embedded multi-die interconnect bridge (EMIB) technology.